library ieee;

use ieee.std_logic_1164.all;

entity compare2bit is

port(

num1: in std_logic_vector(1 downto 0);

num2:

in std_logic_vector(1 downto 0);

less:

out std_logic;

equal:

out std_logic;

greater:

out std_logic

);

end compare2bit;

architecture behavioral of compare2bit is

begin

process(num1,num2)

begin

if

(num1>num2) then

less<='0';

equal<='0';

greater<='1';

elsif

(num1<num2) then

less<='1';

equal<='0';

greater<='0';

else

less<='0';

equal<='1';

greater<='0';

end if;

end

process;

end

behavioral;

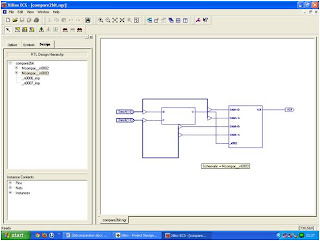

2 bit comparator level 2 Xilinx circuit

2 bit comparator level 3 Xilinx circuit

Truth tablet for 2 bit comparator

|

Num1(0)

|

Num1(1)

|

Num2(0)

|

Num2(1)

|

less

|

equal

|

greater

|

|

0

|

0

|

0

|

0

|

0

|

1

|

0

|

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

|

0

|

0

|

1

|

1

|

1

|

0

|

0

|

|

0

|

1

|

0

|

0

|

0

|

0

|

1

|

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

|

0

|

1

|

1

|

0

|

1

|

0

|

0

|

|

0

|

1

|

1

|

1

|

1

|

0

|

0

|

|

1

|

0

|

0

|

0

|

0

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

0

|

1

|

|

1

|

0

|

1

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

|

1

|

1

|

0

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

0

|

0

|

0

|

1

|

|

1

|

1

|

1

|

1

|

0

|

1

|

0

|

No comments:

Post a Comment